近日,第九屆中國系統級封裝大會(SiP Conference China 2025)在深圳會展中心(福田)隆重開幕。芯和半導體創始人、總裁代文亮博士再次以大會主席身份發表題為《智聚芯能,異構互聯,共贏AI時代機遇》的開幕演講,從產業高度系統闡釋了在AI算力爆發背景下,Chiplet先進封裝技術所面臨的機遇與挑戰,并呼吁產業鏈攜手共建開放協同的Chiplet生態系統。

?

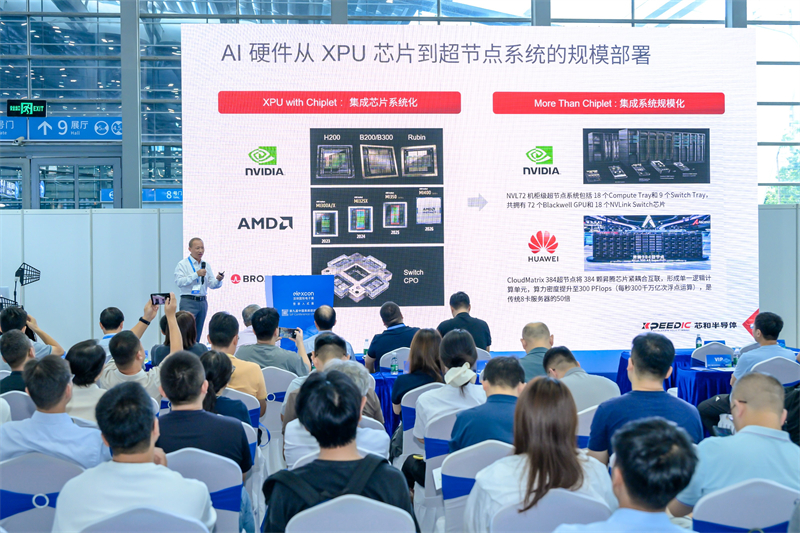

代博士指出:中國系統級封裝大會今年是第九屆。我們一起見證了系統級封裝和先進封裝的高速發展的九年,并迎來了一個新的引爆點:隨著國務院《關于深入實施“人工智能+”行動的意見》的落地,AI人工智能已經被公認為第四次“工業革命”的核心驅動力,應用場景正不斷地從云端訓練推理向海量終端應用滲透,對半導體的算力、存力、運力、電力等性能都提出了巨大的需求和挑戰。然而,隨著摩爾定律逼近物理極限,單純依靠SoC單芯片工藝微縮帶來的性能提升已大幅放緩,系統攻堅已經成為大勢所趨:一方面,芯片系統化——三維芯片Chiplet先進封裝與異構集成正在成為延續算力增長的核心路徑,并被英偉達、AMD、博通等AI芯片巨頭廣泛采用;另一方面,系統規模化——以英偉達NVL72、華為昇騰384機柜級超節點系統為代表的智算系統,正通過硅光在內的更高速互連技術不斷突破scale up和scale out的性能邊界。AI 超節點硬件系統需求與Chiplet集成技術的融合正成為后摩爾時代先進工藝制程瓶頸和算力提升突破的重要方向。

?

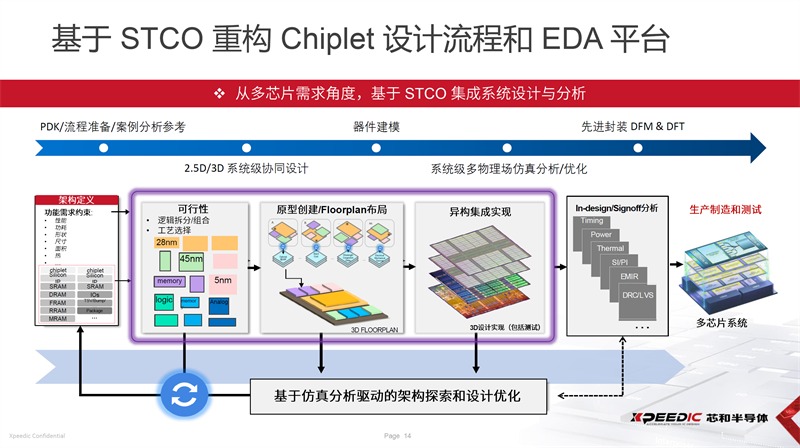

新趨勢意味著有新的問題需要被解決:Chiplet 集成系統面臨高密互連、高速串擾、電-熱-力耦合及反復優化迭代等諸多挑戰,而解決AI超節點硬件系統萬卡級互連拓撲優化、高壓直供電源網絡設計、液冷系統與芯片熱耦合仿真,其復雜度也遠超傳統單芯片設計的能力邊界。這些都需要將設計范式從傳統的單點優化的DTCO(設計工藝協同優化)升級至全鏈路協同的STCO(系統技術協同優化),為國內Chiplet產業鏈帶來了廣闊的發展藍海。

?

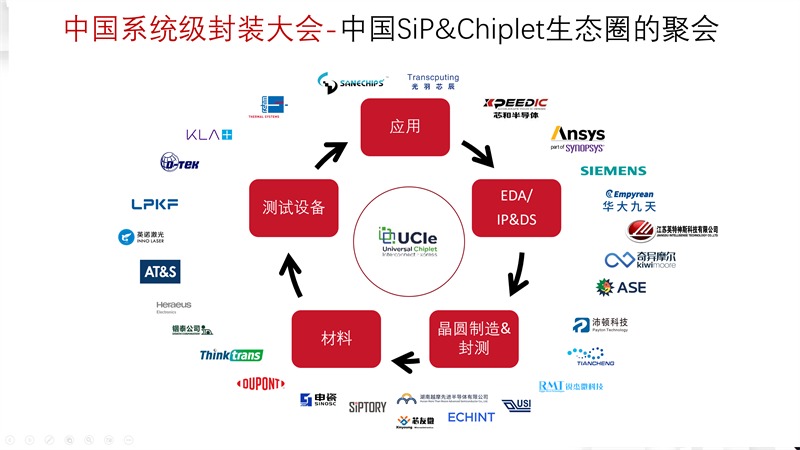

更利好的是,隨著UCIe3.0的發布,以及包括OCP、OIF、3DLink、CCITA等國內外Chiplet標準的逐漸落地和成熟,Chiplet 生態正從“英偉達式”的全封閉模式,走向以開放標準為紐帶的“拼多多模式”,中國在終端場景、整機整合與市場需求方面具備顯著優勢,將推動多元廠商、多工藝節點、多IP來源的異構集成成為主流。代博士呼吁國內Chiplet先進封裝產業鏈每個環節的企業積極躬身入局、強化材料,工藝、設計、流程和EDA工具等跨環節協作,共建“芯片-封裝-系統-應用”的全棧能力,把握AI帶來的時代機遇,并賦能國內AI產業在全球算力競爭中占據主動。

本次大會吸引了幾十家中國系統級封裝與Chiplet先進封裝生態圈的頭部企業共同分享探討。在大會首日的主旨演講環節,除了芯和半導體,還有來自中興微、光羽芯辰、日月光、環旭電子、珠海天成等企業的高管和專家針對Chiplet先進封裝的不同環節做了獨家報告。